broadband plasma (BBP) division // input data adapter (IDA) team

managers: wes nakamura, rish patel

project mentors: frank chao, johnny trinh

tools: systemverilog, questa, vivado, python

company website // division website

intro

KLA (formerly KLA-Tencor) is a prominent toolmaker in the semiconductor industry, specializing in process control and yield management solutions that catch mistakes and ensure chip manufacturing processes are perfect. KLA’s work broadly falls under three main categories:

- Inspection: High-powered optical and electron-beam systems that scan silicon wafers and photomasks for flaws.

- Metrology: Tools that measure the physical dimensions of chip features, such as layer thickness or pattern alignment, to ensure they match the architectural design.

- Data Analytics: Software analyzes the data to identify where manufacturing issues occur.

Examples of KLA inpsection tools.

I worked for KLA’s BBP (broadband plasma) division, which is primarily in charge of “brightfield” inspection tools: versatile, high-end machines capable of scanning wafers with anywhere between visible and deep ultraviolet light. These balance inspection throughput with image fidelity (compared to electron-beam; imagine using a flashlight as compared to a laser beam to see in the dark) for the perfect inspection sweet spot.

You can read more about KLA’s BBP tools in this article!

my work

I helped design and implementat a hardware-accelerated compression pipeline to manage the extreme data throughput of KLA inspection tools. Given the scale of modern semiconductor manufacturing (hundreds of wafers/hour times hundreds of gigabytes/wafer), the JPEG-LS (lossless JPEG) algorithm is implemented on a reconfigurable FPGA array to enable real-time, line-speed processing.

![]()

Pixels A --> D used to predict next pixel X in JPEG-LS.

The implementation utilizes predictive coding: an interpolation model calculates the expected value of subsequent pixels, storing only the difference (residual) between the actual and predicted values. By integrating a “run-length” mode for contiguous regions of similar intensity, the system is optimized for the high-contrast geometries found in photomask and wafer imagery, ensuring efficient storage while maintaining bit-perfect data integrity for future analysis.

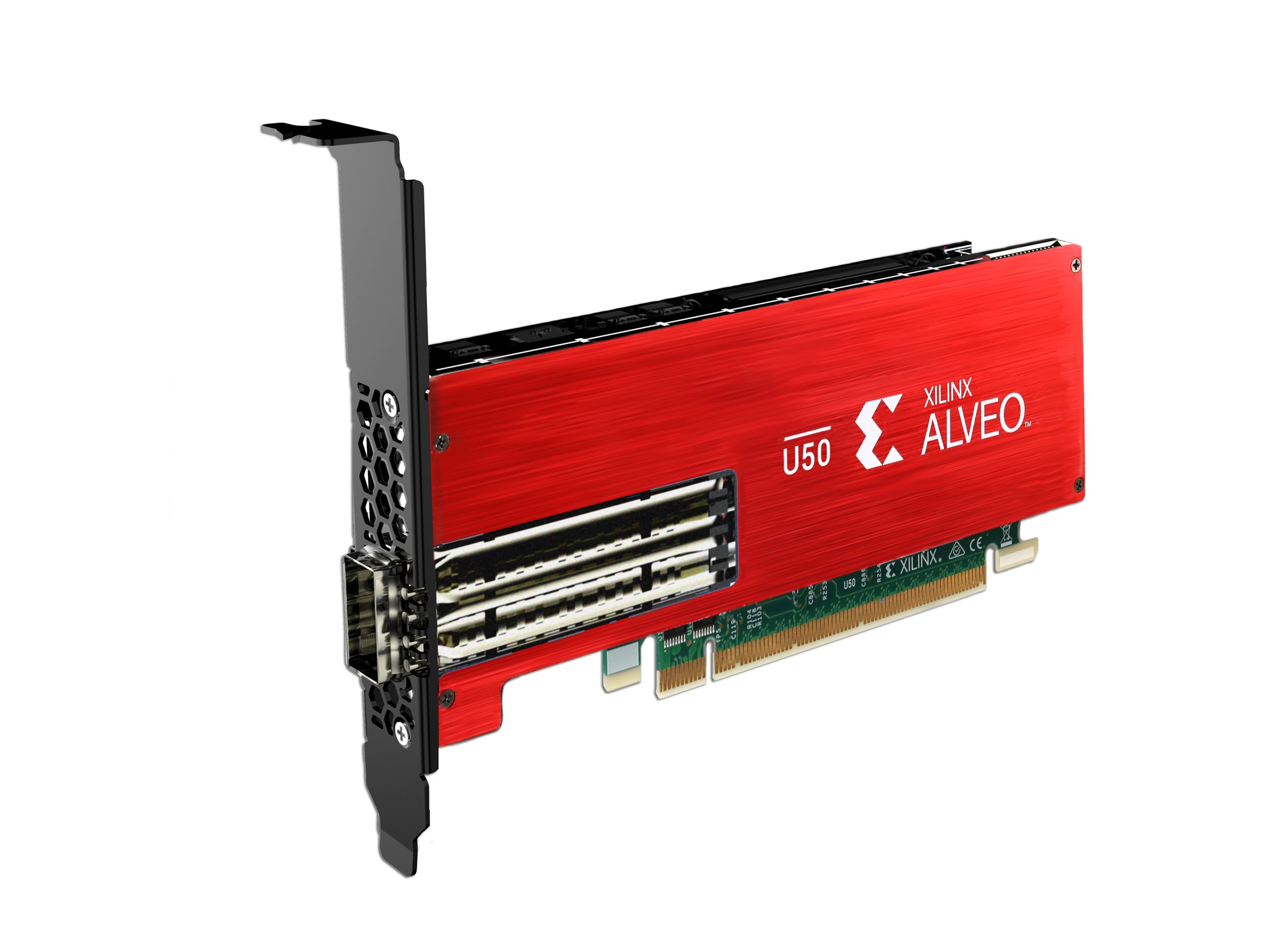

Alveo U50 FPGA accelerator card I targeted for this design.

To meet production demands, I overhauled the initial decompression prototype to use a new JPEG-LS engine design. This involved architecting a system-level framework to manage data distribution and frame reconstruction across multiple JPEG-LS cores. My workflow integrated Vivado’s IP-Integrator for hardware synthesis and Questa for rigorous RTL simulation. I addressed the challenges of frame “stitching” (ensuring seamless data reassembly at the output), optimized hardware utilization, and validated the entire pipeline’s performance using KLA’s hardware benchmarks. This work bridged the gap between a standalone IP block and a fully integrated, hardware-validated acceleration solution.

photos!

Introduction/status cards I made for my "box" (cubicle)

Intern tour of the clean room; me in a bunny suit!

Making electronics kits for local high school students with the KLA foundation

Group photo of all the Milpitas HQ interns

acknowledgements

IDA team photo, August 2025

A massive thank you to the IMC/IDA team for welcoming me with open arms. From competitive pickleball and boba runs to sharing our mechanical keyboard builds and putting fences together, I had an absolute blast.

To my managers, Rish Patel and Wes Nakamura: thank you for the endless mentorship and for trusting me with such a critical project. And to Coen Warmenhoven and Natalie Cooper: thank you for opening the door to this unforgettable summer.

Thanks also to Johhny Trinh for inspiring me to make this website in Jekyll :)